計(jì)算機(jī)硬件開發(fā)是信息技術(shù)領(lǐng)域的核心組成部分,它涉及從基礎(chǔ)組件設(shè)計(jì)到高性能系統(tǒng)集成的全過程。本文將介紹計(jì)算機(jī)硬件開發(fā)的關(guān)鍵要素、當(dāng)前趨勢(shì)以及未來發(fā)展方向,幫助讀者全面了解這一領(lǐng)域。

1. 計(jì)算機(jī)硬件開發(fā)的基礎(chǔ)

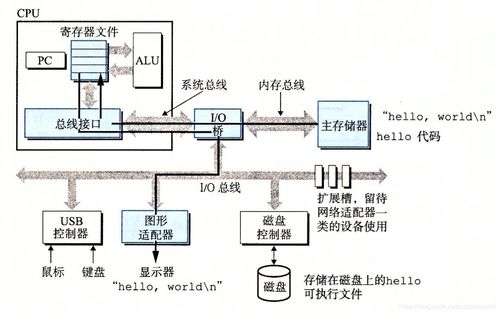

計(jì)算機(jī)硬件開發(fā)包括處理器、內(nèi)存、存儲(chǔ)設(shè)備和外部設(shè)備的設(shè)計(jì)與制造。處理器作為硬件的“大腦”,其設(shè)計(jì)涉及指令集架構(gòu)(如x86或ARM)、微架構(gòu)優(yōu)化以及功耗控制。內(nèi)存開發(fā)則關(guān)注速度與容量的平衡,例如DRAM和SSD技術(shù)的演進(jìn)。主板、電源和散熱系統(tǒng)等支持組件的開發(fā)也至關(guān)重要,它們確保硬件穩(wěn)定運(yùn)行。

2. 開發(fā)流程與工具

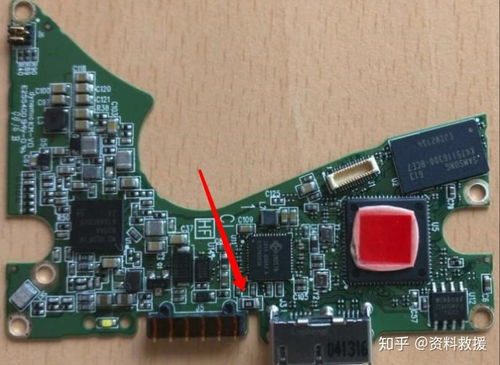

硬件開發(fā)通常遵循系統(tǒng)化的流程:需求分析、設(shè)計(jì)、原型制造、測(cè)試和量產(chǎn)。在設(shè)計(jì)階段,工程師使用EDA(電子設(shè)計(jì)自動(dòng)化)工具進(jìn)行電路仿真和布局規(guī)劃。原型制造依賴于先進(jìn)的半導(dǎo)體工藝,如7納米或5納米制程技術(shù)。測(cè)試環(huán)節(jié)則通過嚴(yán)格的性能、可靠性和兼容性驗(yàn)證,確保硬件符合標(biāo)準(zhǔn)。

3. 當(dāng)前趨勢(shì)與創(chuàng)新

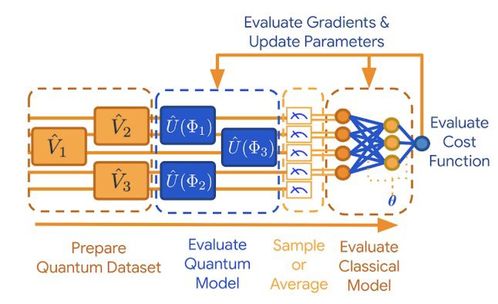

計(jì)算機(jī)硬件開發(fā)呈現(xiàn)出多個(gè)重要趨勢(shì)。人工智能和機(jī)器學(xué)習(xí)的興起推動(dòng)了專用硬件的發(fā)展,例如GPU和TPU,它們優(yōu)化了并行計(jì)算能力。物聯(lián)網(wǎng)(IoT)設(shè)備催生了低功耗、小型化的硬件解決方案。量子計(jì)算和光子計(jì)算等前沿技術(shù)也在探索中,有望突破傳統(tǒng)硬件的性能瓶頸。可持續(xù)性成為熱點(diǎn),開發(fā)人員更注重能源效率和環(huán)保材料的使用。

4. 挑戰(zhàn)與未來展望

盡管硬件技術(shù)不斷進(jìn)步,但仍面臨諸多挑戰(zhàn),包括制程縮小的物理限制、散熱問題以及供應(yīng)鏈的不確定性。硬件開發(fā)將更注重集成化與智能化,例如通過異構(gòu)計(jì)算和神經(jīng)形態(tài)芯片實(shí)現(xiàn)更高的能效。開源硬件(如RISC-V架構(gòu))的普及可能改變行業(yè)生態(tài),促進(jìn)創(chuàng)新協(xié)作。

計(jì)算機(jī)硬件開發(fā)是一個(gè)動(dòng)態(tài)且多學(xué)科的領(lǐng)域,它不僅驅(qū)動(dòng)著計(jì)算能力的提升,還深刻影響著從個(gè)人設(shè)備到超級(jí)計(jì)算機(jī)的方方面面。隨著技術(shù)的演進(jìn),硬件開發(fā)將繼續(xù)在性能、效率和應(yīng)用場(chǎng)景上實(shí)現(xiàn)突破。